다이 본더(Die Bonder) 완벽 가이드: 칩과 기판의 완벽한 결합

Die Bonder

다이 본더:

칩에 안정을 선물하다

쏘잉된 웨이퍼 칩(Die)을 기판(Substrate) 위에 정밀하게 접합하는 공정.

에폭시 도포부터 3D 적층 기술까지, 반도체 패키징의 기초를 만듭니다.

1. 다이 본더(Die Bonder)란? (Deep Dive)

다이 본더(Die Attach System)는 웨이퍼 소싱(Sawing) 공정을 통해 낱개로 잘린 칩(Die)을 픽업하여, 리드프레임이나 PCB 기판 위의 정해진 위치에 고정시키는 반도체 후공정 장비입니다. 과거에는 단순히 에폭시 접착제(Paste)를 사용하여 칩을 붙이는 방식이 주를 이루었으나, 칩이 초박형화되고 적층 기술이 발전함에 따라 DAF(Die Attach Film)를 이용한 필름 접합 방식이나, 범프(Bump)를 이용해 전기적 연결까지 동시에 수행하는 플립칩(Flip Chip) 본딩 기술로 진화하고 있습니다.

2026년형 장비는 특히 HBM(고대역폭 메모리)과 같은 3D 적층 패키지를 위해, 열과 압력을 동시에 가해 금속 간 결합을 유도하는 'TCB (Thermo-Compression Bonding)' 기술과, 솔더 볼 없이 구리 전극을 직접 맞붙이는 '하이브리드 본딩(Hybrid Bonding)' 기술이 적용된 초정밀 장비가 시장을 주도하고 있습니다. 이 과정에서 칩의 기울기(Tilt)와 접착층의 두께(BLT: Bond Line Thickness)를 나노미터 단위로 제어하는 것이 수율과 방열 성능을 결정짓는 핵심 요소입니다.

접합 품질의 3대 핵심 가치

1. 위치 정밀도 (Accuracy)

칩을 놓는 위치가 틀어지면 후속 와이어 본딩 공정이 불가능해집니다. 고속 비전 카메라와 리니어 모터를 이용해 X, Y, θ(회전) 축을 1~5µm 수준으로 정밀 보정합니다.

2. BLT 제어 (Thickness Control)

칩과 기판 사이의 접착제 두께(BLT)가 균일해야 열 방출이 잘 되고 칩이 기울지 않습니다. 본딩 헤드의 압력 센서와 레이저 변위 센서로 실시간 두께를 제어합니다.

3. 픽업 안정성 (Safe Pickup)

웨이퍼 테이프에서 칩을 떼어낼 때 칩이 깨지거나(Die Crack) 스크래치가 나지 않도록, 이젝터 핀(Ejector Pin)의 속도와 콜렛(Collet)의 진공 압력을 정교하게 동기화합니다.

2. 기술 심층 분석: 접합 방식의 종류

액체 상태의 에폭시를 사용하는 전통적 방식과 고체 필름을 사용하는 최신 방식, 그리고 범프를 이용한 플립칩 방식으로 구분됩니다. 제품 특성에 맞는 공법 선택이 중요합니다.

1. 에폭시 본딩 (Epoxy/Paste)

디스펜서로 접착제를 점찍듯 도포하고 칩을 올립니다. 가격이 저렴하고 생산성이 높지만, 접착제가 흘러 넘치거나 두께 제어가 어려워 고집적 패키지에는 한계가 있습니다.

2. 필름 본딩 (DAF / WBL)

웨이퍼 뒷면에 미리 얇은 접착 필름(DAF)을 붙여 놓은 상태에서 칩을 떼어내 열압착합니다. 접착층 두께가 매우 균일하고 오버플로우가 없어 칩 적층(Stacking)에 필수적입니다.

3. 플립칩 본딩 (Flip Chip)

칩의 회로면이 아래로 가도록 뒤집어서, 솔더 볼이나 구리 기둥(Pillar)을 기판 패드에 직접 융착시킵니다. 와이어가 없어 전기적 성능이 우수하고 패키지 크기를 줄일 수 있습니다.

| 구분 | Epoxy / Paste | DAF (Film) | Flip Chip (TCB) |

|---|---|---|---|

| 접착 매체 | 액상 접착제 | 반고체 필름 | 솔더 범프 / Cu Pillar |

| 두께 제어 | 어려움 (유동성) | 매우 우수 (일정함) | 범프 높이에 의존 |

| 주요 용도 | QFP, 리드프레임 | NAND Flash, Memory | AP, CPU, GPU |

| 비용 | 저렴함 | 중간 | 높음 |

3. ROI 분석: UPH와 수율의 상관관계

다이 본딩은 후공정 중 속도가 가장 느린 병목 구간 중 하나입니다. UPH(시간당 생산량)를 높이면서도 위치 정밀도를 유지하는 것이 ROI의 핵심입니다.

| 비교 항목 | 기존 장비 | 최신 고속 본더 | 개선 효과 (Benefit) |

|---|---|---|---|

| UPH (속도) | 4,000 ~ 6,000 | 10,000 ~ 20,000 | 동일 공간 생산량 2배 증대 |

| 정밀도 (Accuracy) | ±25µm | ±5 ~ 10µm | 미세 피치 패키지 대응 |

| 불량률 (Yield) | 위치 틀어짐 발생 | 비전 보정 강화 | 후속 공정(W/B) 에러 감소 |

4. 도입 예산 가이드: 등급별 라인업 (Budgeting)

단순 리드프레임 작업용부터 초정밀 적층용까지, 용도와 정밀도에 따라 장비 가격은 천차만별입니다.

1. 보급형/에폭시 본더 (Standard)

1억 원 ~ 3억 원사양: 리드프레임용, 에폭시 디스펜싱. LED나 일반 IC 패키징에 사용되는 가장 기본적인 모델로 가성비가 좋습니다.

2. 메모리/DAF 본더 (Advanced)

5억 원 ~ 10억 원사양: 12인치 웨이퍼, 박막 칩 핸들링, DAF 부착. 메모리 카드나 USB, SSD용 낸드 플래시 적층에 특화된 장비입니다.

3. 플립칩/TC 본더 (High-End)

15억 원 이상사양: 열압착(TCB) 헤드, 서브 마이크론 정밀도. 고성능 CPU나 AI 반도체 패키징을 위한 최상위 솔루션입니다.

5. Industry 4.0: 스마트 본딩 제어

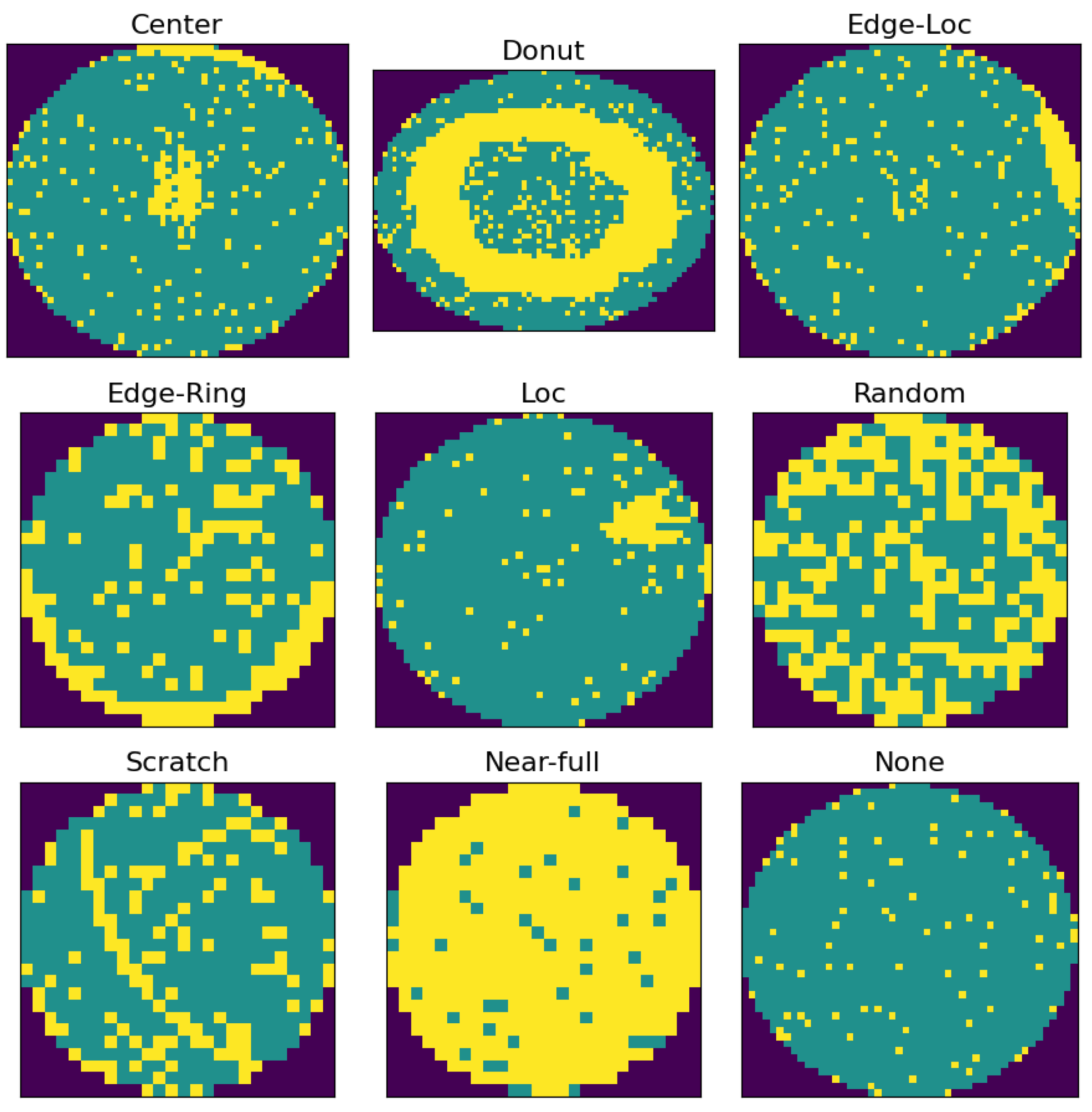

웨이퍼 맵 데이터를 받아 양품 칩만 선별적으로 픽업하고, 본딩 후 위치 정확도를 스스로 검사하여 보정합니다.

- 자동 웨이퍼 교체: 웨이퍼 카세트에서 다 쓴 링 프레임을 배출하고 새 웨이퍼를 로딩하는 과정을 무인 자동화하여 가동률을 높입니다.

- BLT 모니터링: 레이저 센서로 본딩된 칩의 높이를 전수 검사하여, 접착제가 너무 적거나 많게 도포된 불량을 즉시 잡아냅니다.

- 툴 관리 시스템: 픽업 콜렛이나 이젝터 핀의 사용 횟수를 카운트하여, 마모로 인한 픽업 에러가 발생하기 전에 교체 알람을 줍니다.

6. 엔지니어를 위한 예방 정비(PM) 체크리스트

다이 본더의 핵심은 '픽업(Pickup)'입니다. 콜렛(Collet)과 이젝터 핀의 상태, 그리고 디스펜서 노즐 관리가 장비 가동률을 좌우합니다.

| 점검 주기 | 핵심 점검 항목 (Check Point) |

|---|---|

| 매일 (Daily) | 콜렛 팁 오염 및 마모 확인, 디스펜서 노즐 막힘 점검, 진공 압력 체크 |

| 주간 (Weekly) | 이젝터 핀 높이 및 정렬 상태 확인, 웨이퍼 테이블 평탄도 점검 |

| 월간 (Monthly) | 본딩 헤드 압력(Force) 캘리브레이션, 리니어 모터 구동부 구리스 도포 |

7. 실무 FAQ: 현장 엔지니어의 핵심 질문

현장에서 가장 빈번하게 발생하는 칩 깨짐, 픽업 에러, 위치 틀어짐 문제에 대한 원인 분석과 해결 가이드입니다.

Q. 칩을 집을 때 자꾸 깨집니다. (Die Crack)

A. 이젝터 핀이 너무 높게 올라오거나 속도가 빠를 때 발생합니다. 핀 높이와 상승 속도를 줄이고, 가능하다면 멀티 핀 이젝터를 사용하여 충격을 분산시켜야 합니다.

Q. 픽업 미스(Pickup Miss)가 자주 발생합니다.

A. 콜렛 사이즈가 맞지 않거나 진공 라인이 막힌 경우, 또는 웨이퍼 테이프의 점착력이 너무 강한 경우입니다. UV 조사량을 늘려 점착력을 낮추거나 콜렛을 청소하십시오.

Q. 본딩 후 칩이 한쪽으로 기웁니다. (Tilt)

A. 접착제 도포량이 불균일하거나 본딩 헤드의 평탄도가 틀어진 것입니다. 디스펜싱 패턴을 최적화하고, 본딩 툴의 수평(Leveling)을 다시 맞춰야 합니다.

8. 산업별 성공 도입 사례 (Case Study)

메모리 적층, 파워 모듈, 플립칩 패키징 등 다양한 분야에서 다이 본딩 기술이 어떻게 진화하고 있는지 확인해 보십시오.

초박형 칩을 16단 계단식으로 쌓아 올리기 위해, 칩 손상 없는 소프트 픽업 기술과 고정밀 DAF 부착 장비를 도입하여 고용량 SSD 생산성을 확보했습니다.

전기차용 파워 모듈의 방열 성능을 높이기 위해, 일반 에폭시 대신 은(Ag) 페이스트를 사용하고 고압으로 눌러 소결하는 신터링 본더를 적용했습니다.

범프 없이 구리 전극을 직접 맞붙이는 하이브리드 본딩 기술을 도입하여, I/O 밀도를 획기적으로 높이고 차세대 AI 반도체 패키징을 구현했습니다.

9. 도입 후 트러블 사례와 사전 대책 (Troubleshooting)

본딩 불량은 곧바로 자재 폐기로 이어집니다. 위치 오차, 에폭시 퍼짐 등 주요 불량 유형별 설비적 원인과 대처법입니다.

| 장애 현상 (Symptom) | 원인 분석 (Cause) | 해결 (Solution) |

|---|---|---|

| XY 위치 틀어짐 | 비전 인식 오류, PR 마크 오염 | 조명 값 조정, 기판 PR 마크 청소 및 인식률 개선 |

| Epoxy Bleed (퍼짐) | 과도한 도포량, 칩 안착 압력 과다 | 디스펜싱 시간 단축, 본딩 포스(Force) 하향 조정 |

| Missing Die (누락) | 픽업 실패, 진공 누설 | 진공 패드 교체, 이젝터 핀 동기화 타이밍 점검 |